# On the Energy Efficiency and Performance of Irregular Application Executions on Multicore, NUMA and Manycore Platforms

Emilio Francesquini, Márcio Castro, Pedro Henrique Penna, Fabrice Dupros, Henrique Cota De Freitas, Philippe Olivier Alexandre Navaux, Jean-François

Méhaut

# ► To cite this version:

Emilio Francesquini, Márcio Castro, Pedro Henrique Penna, Fabrice Dupros, Henrique Cota De Freitas, et al.. On the Energy Efficiency and Performance of Irregular Application Executions on Multicore, NUMA and Manycore Platforms. Journal of Parallel and Distributed Computing, 2015, 76, pp. 32-48. 10.1016/j.jpdc.2014.11.002 . hal-01092325

# HAL Id: hal-01092325 https://brgm.hal.science/hal-01092325v1

Submitted on 8 Dec 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution - NonCommercial 4.0 International License

# On the Energy Efficiency and Performance of Irregular Application Executions on Multicore, NUMA and Manycore Platforms

Emilio Francesquini<sup>a,b,g</sup>, Márcio Castro<sup>c,d</sup>, Pedro H. Penna<sup>e</sup>, Fabrice Dupros<sup>f</sup>, Henrique C. Freitas<sup>e</sup>, Philippe O. A. Navaux<sup>c</sup>, Jean-François Méhaut<sup>g</sup>

<sup>a</sup>Institute of Computing, University of Campinas (UNICAMP)

Av. Albert Einstein, 1251 - Cidade Universitária- 13083-852 - Campinas, Brazil

<sup>b</sup>Institute of Mathematics and Statistics, University of São Paulo (USP)

Rua do Matão, 1010 - Cidade Universitária - 05508-090 - São Paulo - Brazil

<sup>c</sup>Institute of Informatics, Federal University of Rio Grande do Sul (UFRGS)

Av. Bento Gonçalves, 9500 - Campus do Vale - 91501-970 - Porto Alegre - Brazil

<sup>d</sup>Department of Informatics and Statistics, Federal University of Santa Catarina (UFSC)

Campus Reitor João David Ferreira Lima - Trindade - 88040-970 - Florianópolis - Brazil

<sup>e</sup>Department of Computer Science, Pontifical Catholic University of Minas Gerais (PUC Minas)

Avenida Dom José Gaspar, 500 - 30535-901 - Belo Horizonte - Brazil

<sup>f</sup>Bureau de Recherches Géologiques et Minières (BRGM)

BP 6009, 45060 Orléans Cedex 2, France

<sup>g</sup>CEA-DRT - LIG Laboratory, University of Grenoble

110 Avenue de la Chimie, 38400 Saint-Martin d'Hères, France

#### Abstract

Until the last decade, performance of HPC architectures has been almost exclusively quantified by their processing power. However, energy efficiency is being recently considered as important as raw performance and has become a critical aspect to the development of scalable systems. These strict energy constraints guided the development of a new class of so-called light-weight manycore processors. This study evaluates the computing and energy performance of two well-known irregular NP-hard problems — the Traveling-Salesman Problem (TSP) and K-Means clustering — and a numerical seismic wave propagation simulation kernel — Ondes3D — on multicore, NUMA, and manycore platforms. First, we concentrate on the nontrivial task of adapting these applications to a manycore, specifically the novel MPPA-256 manycore processor. Then, we analyze their performance and energy consumption on those different machines. Our results show that applications able to fully use the resources of a manycore can have better performance and may consume from 3.8x to 13x less energy when compared to low-power and general-purpose multicore processors, respectively.

*Keywords:* Manycore, multicore, NUMA, energy efficiency, performance, TSP, seismic wave propagation, k-means

*Email addresses:* francesquini@ic.unicamp.br (Emilio Francesquini), marcio.castro@inf.ufsc.br (Márcio Castro), pedro.penna@sga.pucminas.br (Pedro H. Penna), f.dupros@brgm.fr (Fabrice Dupros), cota@pucminas.br (Henrique C. Freitas), navaux@inf.ufrgs.br (Philippe O. A. Navaux), jean-francois.mehaut@imag.fr (Jean-François Méhaut)

Preprint submitted to Journal of Parallel and Distributed Computing

August 21, 2014

#### 1 1. Introduction

Demand for higher processor performance led chipmakers to include into their designs solutions that are a combination of brute-force and innovation. The increase of processors cache size, instruction-level parallelism and working frequency have been for the last decades their main tools to accomplish this mission. However, these approaches seem to have reached a point in which they, by themselves, are not sufficent to ensure the steep curve of performance improvement predicted by Moore's Law and expected by the users [1].

An exponential increase in power consumption related to a linear increase in the clock frequency [2] and a higher complexity to design new processors changed the course of development of these new processors. Power consumption has become a critical aspect to the development of 10 both large and small scale systems. This concern is now enough to warrant the research on the 11 use of embedded low-power processors to create the next generation of HPC systems. For in-12 stance, the European Mont-Blanc project [3] was created to evaluate the use of such components 13 in an HPC environment [4]. While these low-power multicore processors usually do not offer 14 the same performance as their regular counterparts, they normally offer better energy-to-solution 15 results. 16

Current highly-parallel processors take this paradigm even further. They normally possess 17 hundreds (sometimes thousands) of cores which execute with high energy efficiency. The execu-18 tion model of these processors usually follows two different approaches. Light-weight manycore 19 processors, such as Tilera Tile-Gx [5] and Kalray MPPA-256 [6], offer autonomous cores and a 20 shared memory execution model. In this case, traditional tools such as POSIX threads are em-21 ployed to accomplish both data and task parallelism. The use these tools may ease the paradigm 22 shift from multicores to manycores, since several parallel applications developed for multicores 23 rely on this model. Differently, Graphics Processing Units (GPUs) follow another approach based 24 on a Single Program, Multiple Data (SPMD) model, relying on runtime APIs such as CUDA and 25 OpenCL. Thus, considerable effort may be necessary to adapt parallel code originally developed 26 for multicores to GPUs. Here we are interested in the former. 27

In this paper we describe three different irregular applications and the necessary adaptations 28 to use them on four distinct hardware platforms. The Traveling Salesman Problem (TSP), the 29 K-Means clustering (K-Means) algorithm, and a Seismic Wave Propagation kernel (Ondes3D). 30 Solutions to the TSP and K-Means problems are NP-hard and, for a large enough instance, the 31 algorithm can be parallelized to make use of an arbitrary number of threads, assuring the com-32 plete use of the chosen platforms. Ondes3D, on the other hand, employs a numeric seismic 33 wave propagation simulation algorithm. These applications were chosen because they represent 34 three different behaviors: CPU-bound (TSP), memory-bound (Ondes3D), and mixed (K-Means). 35 However, while all of them are highly parallelizable, they also reveal important issues related to 36 imbalance and irregularity: the execution course for the same instance of the problem can dras-37 tically change depending on the order and on the number of employed processor cores. 38

We consider two important aspects in this study. The first aspect concerns the programming 39 issues and challenges encountered when adapting these irregular applications for the MPPA-256 40 manycore processor. The use of Network-on-Chip (NoC) for communication and the absence 41 of cache coherence protocols are among the important factors that make the development of 42 parallel applications on this processor not trivial. Additionally, processors such as MPPA-256 43 have important memory constraints, e.g., limited amount of directly addressable memory (2 MB). 44 Furthermore, efficient execution on this processor requires data transfers in conformance to the 45 NoC topology to mitigate the, otherwise high, communication costs. The lessons learned give 46

<sup>47</sup> some insights on what can be faced when adapting parallel applications to manycores.

The second aspect concerns the performance and energy consumption of multicores and 48 manycores. Our experiments were carried out on four different hardware platforms: Intel Xeon 49 E5, SGI Altix UV 2000, Samsung Exynos 5, and Kalray MPPA-256. The first two are composed of 50 general-purpose processors, while the remaining two are based on embedded low-power proces-51 sors. We compare the overall performance of these platforms as well as their power efficiency. 52 Our results show that the energy-to-solution for the same instance of the problem can present 53 important variations between the experimental platforms. For every application, MPPA-256 pre-54 sented the best energy-to-solution, consuming from 3.8x to 6.9x less energy than the second best 55 platform (Exynos 5). When compared to Xeon E5 and Altix UV 2000, MPPA-256 consumed re-56 spectively from 5.7x to 13.1x and from 8.5x to 12.3x less energy. The time-to-solution on the 57 other hand was dominated by the Altix UV 2000 platform. MPPA-256 and Xeon E5 showed approx-58 imately equivalent performances, however with a clear advantage to Xeon E5 for memory-bound 59 applications. With relation to the Altix UV 2000 platform, the execution of the applications were 60 on average from 13.0x to 20.4x, 108.8x to 154.8x and 13.0x to 15.3x slower on the Xeon E5, 61 Exynos 5 and MPPA-256 platforms respectively. Next, we compare the Altix UV 2000 and the 62 MPPA-256 platforms. Although very different from each other, these platforms share some simi-63 larities that give us the opportunity to evaluate important aspects of their scalability and energy 64 efficiency. We concluded that both architectures scale well for the chosen applications. While 65 on low core counts MPPA-256 may have a higher energy-to-solution, it can quickly fill the gap as 66 the increase in the number of cores results in a small increase in the average power consumption. 67 The remainder of this paper is organized as follows. Section 2 outlines the evaluated plat-68 forms. A high-level description of the TSP, K-Means and Ondes3D as well as their algorithms 69 are detailed in Section 3. Next, Section 4 discusses the challenges encountered when passing 70 from multicores to the MPPA-256 manycore processor. Then, Section 5 presents performance 71 and energy efficiency evaluations. Finally, we discuss related works in Section 6 and conclude in 72 Section 7. 73

# 74 **2. Experimental Platforms**

In this section we describe the experimental platforms used in this study. These platforms represent three different classes: general-purpose, embedded and manycore.

#### 77 2.1. General-Purpose

Xeon E5. The Intel Xeon E5 is a 64-bit x86-64 processor. In this study we used a Xeon E5-4640 Sandy Bridge-EP, which has 8 physical cores running at 2.40 GHz. Each core has 32 KB instruction and 32 KB data L1 caches and 256 KB of L2 cache. All the 8 cores share a 20 MB

L3 cache and the platform has 32 GB of DDR3 memory.

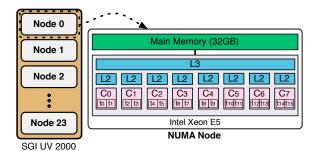

Altix UV 2000. SGI Altix UV 2000 (Figure 1) is a Non-Uniform Memory Access (NUMA) platform designed by SGI. The platform is composed of 24 NUMA nodes. Each node has a Xeon E5-4640 Sandy Bridge-EP processor (with the same specifications of the Xeon E5 platform) and 32 GB of DDR3 memory. This memory is shared in a ccNUMA fashion through SGI's proprietary NUMAlink6 (bidirectional). This high-speed interconnection provides a point-topoint bandwidth of 6.7 GB/s per direction. Overall, this platform has 192 physical cores.

Figure 1: A simplified view of Altix UV 2000.

# 88 2.2. Embedded

Exynos 5. Samsung Exynos 5 is a Multiprocessor System-on-Chip (MPSoC) that implements 89 the recent ARM big.LITTLE heterogeneous computing architecture. In this study we used the 90 ODROID-XU+E board, which features a Samsung Exynos 5 5410 Octa processor. This proces-91 sor integrates a Cortex-A15 quad-core running at 1.6 GHz with a Cortex-A7 quad-core running 92 at 1.2 GHz on the same chip. Both CPUs are connected to 2 GB of LP-DDR3 memory. This 93 processor uses a clustered model approach: the operating system scheduler is only aware of four 94 out of the total of eight processing cores. If at any point in time the load on the four Cortex-95 A7 cores surpasses a pre-established threshold, the processor itself switches the execution to the 96 Cortex-A15 cores. This is done in a way that is transparent to the operating system. The rationale 97 here is that, while the Cortex-A15 cores provide better performance, they also incur in a higher 98 energy utilization and by switching between the two sets of cores energy can be saved. 99

# 100 2.3. Manycore

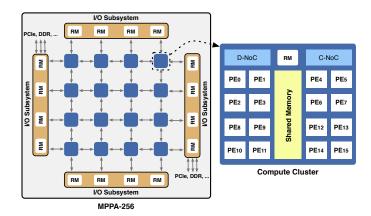

MPPA-256. Kalray MPPA-256 is a single-chip manycore processor developed by Kalray that integrates 256 user cores and 32 system cores. It uses 28nm CMOS technology running at 400 MHz. These cores are distributed across 16 compute clusters and 4 I/O subsystems that communicate through data and control NoCs. This processor targets parallel applications whose programming models fall within the following classes: Kahn Process Networks (KPN), as motivated by media processing; SPMD, traditionally used for numerical kernels; and time-triggered control systems [7, 6].

Figure 2 shows the architecture overview of the MPPA-256. It features two types of cores: 108 Processing Elements (PE) and Resource Managers (RM). Although RMs and PEs implement 109 the same Very Long Instruction Word (VLIW) architecture, they have different purposes: PEs 110 are dedicated to run user threads (one thread per PE) in non-interruptible and non-preemptible 111 mode whereas RMs execute kernel routines and services of NoC interfaces. Operations executed 112 by RMs vary from task and communication management to I/O data exchanges between either 113 external buses (e.g. PCIe) or SDRAM. For this reason, RMs have privileged connections to NoC 114 interfaces. Both PEs and RMs feature private 2-way associative instruction and data caches. 115

PEs and RMs are grouped within compute clusters and I/O subsystems. Each compute cluster

features 16 PEs, 1 RM and a local shared memory of 2 MB, which creates a interconnection with

high bandwidth and throughput between PEs. Each I/O subsystem relies on 4 RMs with a shared

D-cache, static memory and external DDR access (2 GB). Contrary to the RMs available on

Figure 2: A simplified view of the MPPA-256.

compute clusters, the RMs of I/O subsystems also run user code. An important peculiarity of

the MPPA-256 architecture is that it does not support cache coherence between PEs, even among

those in the same compute cluster.

Parallel applications running on MPPA-256 usually follow the *master/worker* pattern. The *master* process runs on an RM of the I/O subsystem and it is responsible for spawning *worker* processes. These processes are then executed on compute clusters and each process may create up to 16 POSIX threads, one for each PE. In other words, the *master* process running on the I/O subsystem must spawn 16 *worker* processes and each process must create 16 threads in order to make full use of the 256 cores.

Compute clusters and I/O subsystems are connected by two parallel NoCs, the Data NoC (D-NoC) and the Control NoC (C-NoC). Both NoCs have bi-directional links, and there is one NoC node per compute cluster, which is controlled by the RM. I/O subsystems, on the other hand, have 4 NoC nodes, each one associated with a D-NoC router and a C-NoC router. The D-NoC is dedicated to high bandwidth data transfers whereas the C-NoC is dedicated to peripheral D-NoC flow control, power management and application messages.

## 135 2.4. Synthesis

As we previously mentioned, Xeon E5, Altix UV 2000, Exynos 5 and MPPA-256 represent dif-136 ferent platform classes. Both Xeon E5 and Altix UV 2000 belong to the class of general-purpose 137 platforms we usually find in servers. These platforms are tuned for performance rather than en-138 ergy efficiency. Differently from those performance-centric platforms, Exynos 5 targets mobile 139 devices in which power is one of the most important concerns. Finally, MPPA-256 belongs to 140 the light-weight manycore platform class. It presents a high density of cores in a single chip but 141 still is more energy efficient than general-purpose processors. In the next section we describe the 142 three applications we used in this paper to analyze the performance and the energy efficiency of 143 these platforms. These applications can also be categorized into distinct behavioral classes what 144 allows us to carry out this study in a comprehensive yet simple manner. 145

#### 146 3. Case Studies

Application execution performance can vary a lot depending on the hardware platform on 147 which they are being executed. These pieces of software are normally categorized by their be-148 havior taking into account the execution aspect that influences their performance the most. For 149 instance, an application in which the time used for memory accesses is a performance bottleneck 150 is said to be memory-bound. Similarly, an application in which the execution bottleneck is the 151 computation time is said to be CPU-bound. As we show in Section 5, an application that on 152 153 a hardware architecture is CPU-bound can become memory-bound on other architectures if the 154 underlying hardware characteristics are not taken into consideration.

To highlight the impact different amounts of computation and communication can make on the execution performance and the energy efficiency of the experimental hardware platforms, we chose three applications with three distinct behaviors (CPU-bound, memory-bound and mixed). We now detail these applications further.

# 159 3.1. Traveling-Salesman Problem

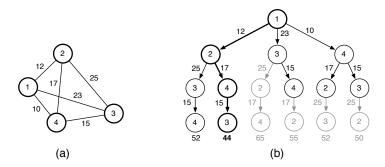

The TSP consists in solving the routing problem of a hypothetical traveling- salesman. Such a route must pass through *n* cities, only once per city, return to the city of origin and have the shortest possible length. It is a very well studied NP-hard problem. More formally, the problem could be represented as a complete undirected graph G = (V, E), |V| = n where each edge  $(i, j) \in E$  has an associated cost  $c(i, j) \ge 0$  representing the distance from the city *i* to *j* (Figure 3a). The goal is to find a hamiltonian cycle with minimum cost that visits each city only once and finishes at the city of departure.

Figure 3: Example of TSP with 4 cities.

There are several different approaches to solve this problem [8]. These solutions normally employ brute force, simple or complex heuristics, approximation algorithms or a mix of them. We are not going to detail the different available approaches since we are after the evaluation and performance comparison of an embarrassingly parallel non-numerical application across different architectures. Therefore, we use a brute force exact algorithm based on a simple heuristic [9]. We first explain the sequential version of our algorithm, then we explain how we extended it to work with multiple threads. Finally, we present its distributed version. 174 3.1.1. Sequential Algorithm

The sequential version of the algorithm is based on the branch and bound method using brute

force. Algorithm 3.1 outlines this solution. It takes as input the number of cities and a cost matrix, and outputs the minimum path length.

#### Algorithm 3.1: TSP SEQUENTIAL(*n\_cities*, costs)

```

\begin{array}{l} \textbf{global } min\_path \\ \textbf{procedure } TSP\_SOLVE(last\_city, current\_cost, cities) \\ \textbf{if } cities = \emptyset \\ \textbf{then return } (current\_cost) \\ \textbf{for each } i \in cities \\ \textbf{do} \\ \begin{cases} new\_cost \leftarrow current\_cost + costs[last\_city, i] \\ \textbf{if } new\_cost < min\_path \\ \textbf{then } \begin{cases} new\_min \leftarrow TSP\_SOLVE(i, new\_cost, cities \setminus \{i\}) \\ ATOMIC\_UPDATE\_IF\_LESS(min\_path, new\_min) \end{cases} \\ \end{array}

```

$\begin{array}{l} min\_path \leftarrow \infty \\ \texttt{TSP\_SOLVE}(1, 0, \{2, 3, ..., n\_cities\}) \\ \textbf{output} \ (min\_path) \end{array}$

This algorithm does a depth-first search looking for the shortest path and has complexity 178 O(n!). It does not explore paths that are already known to be longer than the best path found 179 so far, therefore discarding fruitless branches. Figure 3b shows this behavior. The shaded edges 180 are those that the algorithm does not follow, since a possible solution that includes them would 181 be more costly than the one it has already identified. This simple pruning technique greatly 182 improves the performance of the algorithm. However, it also introduces irregularities into the 183 search space. The search depth needed to discard one of the branches depends on the order in 184 which the branches were searched. 185

## 186 3.1.2. Multi-threaded Algorithm

The multi-threaded version of the algorithm works by creating a queue of tasks from which 187 each thread takes the jobs to be executed. A task is nothing more than one of the branches of 188 the search tree. The generation of the tasks is done sequentially since the time needed to do 189 it is negligible. As soon as one thread runs out of work, it takes a new task from the queue. 190 The number of tasks to be generated is a function of the number of threads and is defined by 191 the max\_hops parameter. This is the minimum number of levels of the search tree that must 192 be descended so that there is a minimum (parameterizable) number of tasks per thread. The 193 total number of tasks as a function of levels l and cities n can be determined by the following 194 recurrence relation (Equation 1) which is defined for  $0 \le l < n$ . 195

$$t(l,n) = \begin{cases} 1 & l = 0\\ t(l-1,n) * (n-l) & \text{otherwise} \end{cases}$$

(1)

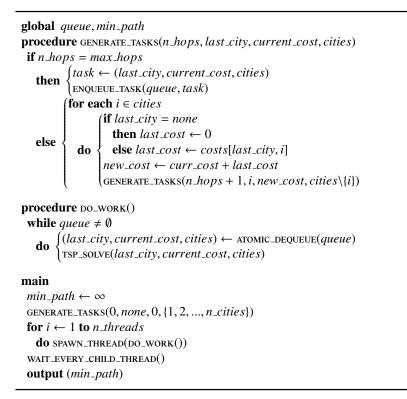

Algorithm 3.2 shows the pseudo-code for this approach. This algorithm also receives as a parameter the number of threads  $n_{threads}$  to be used.

**Algorithm 3.2:** TSP Multi-threaded(*n\_cities*, *costs*, *n\_threads*, *max\_hops*)

198 3.1.3. Distributed Algorithm

The distributed algorithm is similar to the multi-threaded version. It receives as an additional 199 parameter the number of distributed peers to be used. The number of peers and the number of 200 threads define the total number of lines of execution. For each peer, n\_threads will be created, 201 thus totaling  $n_{threads} \times n_{peers}$  threads. Inside each peer, the execution is nearly identical to that 202 of the multi-threaded case. The only difference is that when the *min\_path* is updated, this update 203 is broadcasted to every other peer so they can also use it to optimize their execution. At the end 204 of the execution, one of the peers (typically the 0-th) prints the solution. The final solution might 205 have been discovered by any one of the peers, however all of them are aware of it due to the 206 broadcasts of each discovered min\_path. 207

To avoid two peers working on the same subproblem, each peer *peer\_id* only works on the 208 tasks which were assigned to it. To do so, we specify the desired number of partitions per 209 peer. We also specify the percentage of the tasks that will be distributed in the beginning of 210 the execution. Afterwards, as the peers run out of work, they will ask a master peer for more 211 partitions. To reduce communication, the master peer sends sets of partitions of decreasing size 212 at each request [10]. The rationale behind it is that, as the task sizes are irregular, distributing 213 a smaller number of partitions during the end of the execution might decrease the imbalance 214 between the peers. In this case, for each request the master peer sends a set of partitions S and 215 the peer *peer\_id* will work on the tasks such that *task\_index* mod *n\_partitions*  $\in$  S. Since the 216 task generation is done locally, the amount of transferred data can be minimized. 217

As a runtime optimization, only one thread per peer becomes responsible for asking for more partitions when the peer runs out of work. Once this thread receives a new partition from the master peer, it generates and populates the peer's task queue with new tasks. During the generation of these tasks, the remaining  $n\_threads - 1$  threads can begin to process tasks as soon as they are enqueued, without the need to wait for the end of the task generation. This behavior is further discussed in Section 5.5.

#### 224 3.2. The K-Means Clustering Problem

Clustering analysis plays an important role in different fields, including data mining, pattern

recognition, image analysis and bioinformatics [11]. In this context, a widely used and studied

clustering approach is the K-Means clustering.

Formally, the K-Means clustering problem can be defined as follows. Given a set of n points in a real d-dimensional space, the problem is to partition these n points into k partitions, so as to minimize the mean squared distance from each point to the center of the partition it belongs to.

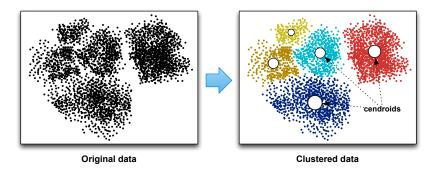

<sup>231</sup> Figure 4 illustrates an instance of this problem.

Figure 4: An example of K-Means with 5 partitions.

Several distinct heuristics have been proposed to address the K-Means clustering problem [12, 13]. One of the most widely employed is the Lloyd's algorithm [14], also known as K-Means algorithm. Such heuristic is based on an iterative strategy that finds a locally minimum solution for the problem. In our work we used this algorithm as a case study. In the following subsections, we first present the sequential version of the algorithm and then we introduce and explain our parallel and distributed versions. 238 3.2.1. Sequential Algorithm

The sequential version of K-Means is shown in Algorithm 3.3. The main idea is to use the notion of minimum Euclidean distance to iteratively partition the data points. The algorithm takes as input the set of data *points*, the number of partitions k, and the minimum accepted distance, *mindistance*, between each point and the partition's center (centroids). Upon completion, the algorithm returns the partitions themselves.

Algorithm 3.3: K-MEANS SEQUENTIAL (points, k, mindistance)

global partitions

```

procedure POPULATE()

for each pnt ∈ points

do pnt.partition ← NEAREST(pnt, partitions)

```

```

procedure COMPUTE_CENTROIDS()

for each part ∈ partitions

do part.centroid ← COMPUTE_MEAN(part.population)

```

#### main

```

RANDOM_POPULATE(partitions, points)

COMPUTE_CENTROIDS()

repeat

{POPULATE()

COMPUTE_CENTROIDS()

until HAS_CHANGED() and TOO_FAR()

return (partitions)

```

The sequential K-Means algorithm works as follows. Initially, data points are evenly and randomly distributed among the k partitions, and the initial centroids are computed. Then, the data points are re-clustered into partitions taking into account the minimum Euclidean distance between them and the centroids — points are assigned to the nearest partition. Next, the centroid of each partition is recalculated taking the mean of all points in the partition, and the whole procedure is repeated until no centroid is changed and every point is farther than the minimum accepted distance.

It is worthy to note that this algorithm presents a natural irregularity: at any time during the execution, the number of points within each partition (population) may differ, implying different recalculation times for each partition's centroid.

### 254 3.2.2. Multi-threaded Algorithm

The multi-threaded version of the K-Means algorithm is presented in Algorithm 3.4. Compared to the sequential algorithm, it takes an additional parameter, *t*, that specifies the total number of execution flows. The strategy adopted is to assign to each thread an unique range of points and partitions, and split the algorithm in two phases. In the first phase, each thread re-clusters its

- $_{259}$  own range of points into the k partitions. In the second phase, each thread works in its own range

- <sup>260</sup> of partitions, in order to recalculate centroids.

**Algorithm 3.4:** K-MEANS MULTI-THREADED(*points*, *k*, *mindistance*, *t*)

global partitions

procedure DO\_KMEANS(work) repeat {POPULATE(work.first\_point, work.last\_point) COMPUTE\_CENTROIDS(work.first\_partition, work.last\_partition) until HAS\_CHANGED() and TOO\_FAR()

# main

$\begin{aligned} & \texttt{RANDOM\_POPULATE}(partitions, points) \\ & \texttt{COMPUTE\_CENTROIDS}(partitions.first, partition.last) \\ & \texttt{for } i \leftarrow 0 \texttt{ to } (t-1) \\ & \texttt{work.first\_point} \leftarrow (i \times num\_points \div t \\ & \texttt{work.last\_point} \leftarrow (i+1) \times num\_points \div t \\ & \texttt{work.last\_partition} \leftarrow (i \times k \div t \\ & \texttt{work.last\_partition} \leftarrow (i+1) \times k \div t \\ & \texttt{spawn\_THREAD}(\texttt{DO\_KMEANS}(work)) \\ \end{aligned} \end{aligned}$

The multi-threaded version of the algorithm still presents some important execution irregularities. Although the range of points and partitions are evenly distributed among the working threads, the amount of work for each thread may vary during each iteration, since for the duration of the second phase more populated partitions end up requiring more operations to have their centroids recalculated.

266 3.2.3. Distributed Algorithm

The distributed algorithm described in this section is widely used in practice [11, 15, 16] and a scalability analysis for this algorithm can be seen in the work by Rodrigues *et. al.* [17]. Compared to the multi-threaded algorithm, the distributed K-Means algorithm takes an additional parameter *p* that specifies the number of distributed peers to be used. Each peer by itself spawns *t* working threads, so the total number of threads equals to  $p \times t$ .

The strategy employed in this algorithm is to first distribute the data points and replicate the data centroids among peers, and then to loop over a two-phase iteration. In the first phase, partitions are populated, as in the multi-threaded algorithm, and in the second phase, data centroids are recalculated. For this recalculation, first each peer uses its local data points to compute partial centroids, *i.e.*, a partial sum of data points and population within a partition. Next, peers exchange partial centroids so that each peer ends up with the partial centroids of the same partitions. Finally, peers compute their local centroids and broadcast them.

One could argue that it would be possible to remove some of the irregularity from the multi-279 threaded version if we used the same partial centroid calculation technique used by the distributed 280 implementation. The multi-threaded version of the algorithm splits the computation in two inde-281 pendent phases: populate partitions and compute centroids of partitions. The main advantage of 282 using this approach is that it requires fewer thread synchronization structures, when compared 283 to the distributed implementation. However, this multi-threaded implementation may introduce 284 some irregularity in the application. Instead, if we adopted the same technique used by the dis-285 tributed approach, we could split the overall work into smaller tasks and decrease some of the 286 irregularity. However, the decreased irregularity would be achieved at the expense of an impor-287 tant increase in the cost of synchronization structures. 288

Nevertheless, the irregularity itself is closely related to the working data set: if partitions are too unbalanced, irregularity is strongly present; whereas if points are evenly distributed among partitions, irregularity is not so sharply presented. In both the multi-threaded and distributed algorithms, we work with a uniformly distributed random data set, and thus irregularity is not strongly present. Considering that, if we adopted the distributed approach in the multi-threaded implementation, we would further decrease irregularity, but the performance gains obtained by that strategy are quickly overcome by the additional synchronization procedures causing, in fact, performance degradation.

#### 297 3.3. Seismic Wave Propagation

Understanding the wave propagation with respect to the structure of the Earth lies at the core of many analysis both in the oil and gas industry and for quantitative seismic hazard assessment. In this paper the earthquake process is described as elastodynamics and we use a finite-differences scheme for solving the wave propagation problem in elastic media [18]. This approach was first proposed in 1970 and since then it has been widely employed due to its simple formulation and implementation. In this section we describe the governing equations and discuss some of their standard sequential and parallel implementations.

<sup>305</sup> The seismic wave equation in the case of an elastic material is:

$$\rho \frac{\partial v_i}{\partial t} = \frac{\partial \sigma_{ij}}{\partial j} + F_i \tag{2}$$

Additionally, the constitutive relation in the case of a isotropic medium is:

$$\frac{\partial \sigma_{ij}}{\partial t} = \lambda \delta_{ij} \left( \frac{\partial v_x}{\partial x} + \frac{\partial v_y}{\partial y} + \frac{\partial v_z}{\partial z} \right) + \mu \left( \frac{\partial v_i}{\partial j} + \frac{\partial v_j}{\partial i} \right)$$

(3)

<sup>307</sup> Where indices *i*, *j*, *k* represent a component of a vector or tensor field in Cartesian coordinates <sup>308</sup> (*x*, *y*, *z*), *v<sub>i</sub>* and  $\sigma_{ij}$  represent the velocity and stress field respectively, and *F<sub>i</sub>* denotes an external <sup>309</sup> source force.  $\rho$  is the material density and  $\lambda$  and  $\mu$  are the elastic coefficients known as Lamé <sup>310</sup> parameters. A time derivative is denoted by  $\frac{\partial}{\partial t}$  and a spatial derivative with respect to the *i*-th <sup>311</sup> direction is represented by  $\frac{\partial}{\partial t}$ . The Kronecker symbol  $\delta_{ij}$  is equal to 1 if *i* = *j* and zero otherwise.

312 3.3.1. Sequential Algorithm

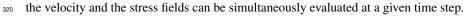

As mentioned before, the finite differences method is one of the most popular techniques to solve the elastodynamics equations and to simulate the propagation of seismic waves [18, 19]. One of the key features of this scheme is the introduction of a staggered-grid [20] for the discretization of the seismic wave equation. Indeed, all the unknowns are evaluated at the same location for classical collocated methods

over a regular Cartesian grid whereas the staggered grid leads to a shift of the derivatives by half

<sup>319</sup> a grid cell (Figure 5). The equations are rewritten as a first-order system in time and therefore the valuation and the stress folds can be simple a well-stress of the stress folds.

Figure 5: Elementary 3D cell of the staggered grid and distribution of the stress ( $\sigma$ ) and the velocity (v) components.

The computational procedure is described in Algorithm 3.5. Inside the time step loop, the first triple nested loop is devoted to the computation of the velocity components, and the second loop reuses the velocity results of the previous time step to update the stress field. For instance, the stencil applied for the computation of the velocity component in the *x*-direction is given by Equation 4. Exponents *i*, *j*, *k* indicate the spatial direction,  $\sigma^{ijk} = \sigma(i\Delta s, j\Delta s, k\Delta s)$ ,  $\Delta s$ corresponds to the space step,  $\Delta t$  to the time step and  $a_1, a_2$  and  $a_3$  are defined as three constants.

**Algorithm 3.5:** Sequential Seismic Wave Propagation Kernel( $\sigma$ , v)

for  $x \leftarrow 1$  to x\_dimension do  $\begin{cases}

for <math>y \leftarrow 1 \text{ to } y \text{-dimension} \\

do \begin{cases}

for <math>z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for x \leftarrow 1 \text{ to } x \text{-dimension} \\

do \\

for y \leftarrow 1 \text{ to } y \text{-dimension} \\

do \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension} \\

do \\

for z \leftarrow 1 \text{ to } z \text{-dimension}$

One particularity of the three-dimensional simulation of seismic wave propagation is the consideration of a finite computing domain whereas the physical problem is unbounded. Additional numerical conditions are then required to absorb the energy at the artificial boundaries. At the lateral and bottom edges of the three-dimensional geometry, a specific set of equations is implemented. For instance, the classical Perfectly Matched Layer (PML) relies on the implemen-

- tation of a sponge numerical function that provides exponential attenuation in the nonphysical

- region [21]. A fixed size of ten grid points is chosen for the thickness of this layer (represented

- in gray color in Figure 6) and the CPU-cost ratio observed between a boundary grid point and a

- <sup>335</sup> physical domain point varies from two to four.

$$v_{x}^{(i+\frac{1}{2})jk} \left(l+\frac{1}{2}\right) = v_{x}^{(i+\frac{1}{2})jk} \left(l-\frac{1}{2}\right) + a_{1} F_{x}^{(i+\frac{1}{2})jk} + a_{2} \left[\frac{\sigma_{xx}^{(i+1)jk} - \sigma_{xx}^{ijk}}{\Delta x} + \frac{\sigma_{xy}^{(i+\frac{1}{2})(j+\frac{1}{2})k} - \sigma_{xy}^{(i+\frac{1}{2})(j-\frac{1}{2})k}}{\Delta y} + \frac{\sigma_{xz}^{(i+\frac{1}{2})j(k+\frac{1}{2})} - \sigma_{xz}^{(i+\frac{1}{2})j(k-\frac{1}{2})}}{\Delta z}\right] - a_{3} \left[\frac{\sigma_{xx}^{(i+2)jk} - \sigma_{xx}^{(i-1)jk}}{\Delta x} + \frac{\sigma_{xy}^{(i+\frac{1}{2})(j+\frac{3}{2})k} - \sigma_{xy}^{(i+\frac{1}{2})(j-\frac{3}{2})k}}{\Delta y} + \frac{\sigma_{xz}^{(i+\frac{1}{2})j(k+\frac{3}{2})} - \sigma_{xz}^{(i+\frac{1}{2})j(k-\frac{3}{2})}}{\Delta z}\right]$$

(4)

This numerical kernel leads to several challenges when considering its implementation on parallel architectures. The load imbalance must be tackled with different strategies adapted to shared or distributed architectures. This first level of irregularity could be worsened by the memory-bound nature of this numerical stencil and advanced strategies must therefore be used to maximize the performances on hierarchical platforms.

#### 341 3.3.2. Multi-threaded Algorithm

On shared-memory architectures, a popular way to extract parallelism is to exploit the triple 342 nested loops coming from the three dimensions of the problem under study. This allows a very 343 straightforward use of OpenMP directives. However, two levels of irregularity should be consid-344 ered with this straightforward implementation. Firstly, the imbalance coming from the absorbing 345 boundary conditions could be partially addressed by using a dynamic schedule across the loop it-346 erations. This leads to significant improvements in the distribution of the load [22]. This solution 347 comes at the expense of introducing an irregular access of the data with higher NUMA penalties 348 on hierarchical platforms. In this paper we tackled the imbalance by exploiting a static strategy 349 along with an intelligent memory allocation policy. Basically, we guarantee that the memory 350 accessed by each thread is allocated close to the thread. This reduces considerably the latencies 351 in NUMA platforms. In the same sense, advanced runtime systems also provide good results in 352 order to improve threads and memory mapping [23]. 353

# 354 3.3.3. Distributed Algorithm

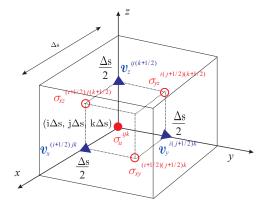

On distributed memory architectures, most standard parallel implementations of the elasto-355 dynamics equations are based on cartesian grid decomposition. Although our code is different, 356 our approach is very similar to that used by Cui et al. [24] and Furumura and Chen [25]. Our 357 distributed algorithm works by decomposing the computational domain into sub-domains  $D_i$  in 358 such a way that each sub-domain is mapped to one peer. Inside each peer, the execution is nearly 359 identical to that of the multi-threaded case. The difference is that peers need to communicate 360 with their neighbors to exchange boundary data. Figure 6 shows this decomposition with  $3\times3$ 361 subdomains with an equal number of grid points in each. 362

This strategy can be optimized by using non-blocking communications among peers and by overlapping communications and computations. For instance, we first compute the boundary grid points located between neighbors. Then, these values are exchanged between neighboring peers using non-blocking communications. During this exchange phase, each peer computes its inner points in parallel.

Figure 6: Distributed implementation of the seismic wave propagation kernel with a  $3\times3$  decomposition. The gray regions represent the irregular absorbing boundary condition layers.

This decomposition also implies an irregular load between peers, due to the absorbing boundary condition layers. The irregularity of the distributed algorithm is investigated by *Tesser et al.* [26]. In this case, quasi-static decomposition, adaptive mesh refinement or parallel mesh partitioning are standard techniques that intend to balance computations. In this paper we applied the former technique [27].

### 373 3.4. General Considerations

In this section we described the three applications we use as case studies. We presented 374 TSP, a CPU-bound application, in which only a small amount of data needs to be kept during the 375 execution. In the multi-threaded algorithm threads rarely communicate, and when they do so they 376 only exchange small amounts of data. Conversely, Ondes3D is a memory-bound application that 377 accesses vast amounts of memory during its execution. Threads on the multi-threaded version 378 often communicate to exchange information about the borders of the current data set on which 379 they are working. K-Means is halfway between these two applications: the time used for data 380 accesses is well balanced with computation time. In the multi-threaded version each thread has 381 its own set of data that is synchronized at the end of each iteration. 382

Both K-Means and TSP present strong irregularity which translates to unpredictable execution times. The irregularity itself is linked to the problem (and to the input) and the chosen algorithm can only do so much to try to alleviate this issue during runtime [28]. These kind of applications have a strong need for dynamic load balancing to manage the irregularity. Weak irregularity is also present in these applications and it is normally associated to the chosen algorithms, data structures, and load-balancing strategy. With varying degrees of effort (and success) these weak irregularities might lightened by distinct implementation choices.

Contrary to TSP and K-Means, Ondes3D is an application that presents only weak irregular-390 ity. It is a predictable application in the sense that the total number of operations and communi-391 cations is known in advance. For this application, given the input, it is even possible with some 392 effort to statically perform the load balancing before the actual execution. However, in practice, 393 this kind of approach seems to be left aside in favor of a dynamically load-balanced stencil based 394 approach. In this kind of solution the irregularity arises from the data and their shape (at the bor-395 der of computation domain and inside the computation domain) and not from the load-balancer. 396 The load-balancer is, in fact, the responsible for trying to ensure a more regular execution. 397

By taking into consideration these three applications and the three distinct hardware architectures used in our experimental evaluations, we can draw comprehensive (yet straightforward) conclusions about execution performance and energy efficiency of these applications on the distinct hardware platform classes.

Manycores have several distinctive features that must be considered so that applications can achieve good performance. In the next section we present the adaptations we did to the applications we just presented in order to achieve an efficient execution.

#### 405 4. Adapting Irregular Applications for Manycores

The adaptation of existing distributed applications to manycores such as the MPPA-256 can be straightforward, as in the case of K-Means. On the other hand, some applications as the TSP and Ondes3D demand much more effort. In this section we describe the adaptations these applications had to go through to efficiently execute on the MPPA-256 manycore.

## 410 4.1. TSP

Section 3.1 presented some insights into the algorithms for the resolution of the TSP. However, efficiently passing from multicores to manycores might be a nontrivial task. There are several reasons for that, the most evident being the natural architectural differences between these platforms. These differences usually force us to make adaptations to the code. In this section, we discuss these architectural aspects and adaptations as well as the rationale behind them.

POSIX threads are supported by all experimental platforms. This allowed us to execute the application on Xeon E5, Altix UV 2000, and Exynos 5 using exactly the same code. In our implementation, the global variable *min\_path*, defined by Algorithm 3.1, is implemented using a simple shared variable that is accessed by every thread. The function ATOMIC\_UPDATE\_IF\_LESS() is therefore implemented using a regular POSIX lock.

Unfortunately, this common solution is not appropriate to the MPPA-256 platform since it 421 does not possess coherent caches. Despite the fact that the update of *min\_path* works as it should 422 (on the MPPA-256 platform the POSIX lock implementation invalidates the whole cache) and the 423 final path length is correct, each one of the worker threads might be using a stale value of the 424 *min\_path* variable for a long time (in the worst case until the end of its execution) and wasting 425 time on fruitless branches of the search tree. This means that, although correct, the execution 426 might be severely slowed down. To correct it, we have used platform specific instructions that 427 allow us direct access to the local memory of the cluster, bypassing the cache (\_\_builtin\_k1\_ lwu and \_\_builtin\_k1\_swu to load/store data from/to the local memory, respectively). The cost 429 of reading the variable in this manner is clearly higher than using the value stored in the caches 430 (reading from memory takes 8 cycles whereas reading from cache takes at most 2 cycles). Yet, 431 the performance improvement due to the better pruning of the search tree largely outweighs the 432 additional cost. 433

In order to efficiently exploit the MPPA-256 platform, we needed to use every cluster of the chip. These clusters do not have a global memory space hence the need for the distributed version of the algorithm. Conversely, Altix UV 2000 platform has a global memory space, however, as the communications between the NUMA nodes are done through the NUMAlink6 interconnection, we can make a better use of this system by keeping the memory near the threads that use it and avoid using the link to perform anything but global synchronizations and *min\_path* propagation. The distributed algorithm fits perfectly in this scenario.

In general, the distributed algorithm used by MPPA-256 and Altix UV 2000 is the same. Peers in 441 the MPPA-256 platform take the form of compute clusters while in the Altix UV 2000 platform each 442 peer is represented by a NUMA node. The difference lies on the implementation of the *min\_path* 443 broadcast and the task distribution. On the Altix UV 2000 platform, the implementation is based 444 on shared memory using locks and condition variables. On the other hand, the implementation 445 for the MPPA-256 platform is more complex. Since there is no shared memory between clusters, 446 we employ asynchronous message exchanges. These message exchanges take the form of remote 447 memory write operations. This can be done using proprietary MPPA-256 low-level system calls 448 that allow a thread in a cluster to write to the memory of any other cluster on the chip. In both 449 cases, the local value of the *min\_path* variable is updated atomically. However, due to the time 450 needed to broadcast a new value, some threads might use a stale value for a short time until the 451 broadcast is completed. 452

#### 453 4.2. K-Means

454 Section 3.2 presented the K-Means problem as well as three different approaches to solve 455 it. In this section we discuss how the solution of this problem was adapted to the manycore 456 architecture used in this work.

Xeon E5, Altix UV 2000 and Exynos 5 are platforms in which all cores have access to a global 457 shared memory space. Additionally, these platforms support OpenMP. Therefore, for these plat-458 forms we employed the multi-threaded solution presented in Algorithm 3.4 using OpenMP for 459 parallelization. Unfortunately this same solution is not appropriate for the MPPA-256 platform. 460 Even though MPPA-256 supports OpenMP, cores in the MPPA-256 platform are grouped into 16-461 core clusters. Cores in the same cluster have access to the local shared memory but have no 162 access to memory present on the remaining clusters. For this reason we had to embrace the dis-463 tributed version of the application in order to explore the full computational power provided by this platform. 465

Despite the distributed algorithm presented in Section 3.2.3 being more appropriate to the 466 MPPA-256 platform than the multi-threaded version, it has some characteristics that limit its direct 467 use on this platform. Local memory available to each cluster (2 MB, of which 500 KB are used by 468 the operating system) creates a strong constraint on the number of points that can be dealt with by 469 each cluster. Even though the 32 MB ( $16 \times 2$  MB) of memory available in the computing clusters 470 could store a reasonably sized workload, a static distribution of points at the initialization of the 471 algorithm would totally disregard the 2 GB of memory available at the I/O subsystem. Therefore, 472 we employed a dynamic solution for the distribution of points to be able to work with a number 473 of points that is only limited by the amount of memory available at the I/O subsystem. 474

In order to do so, we implemented a variation of the distributed algorithm using a dynamic 475 one-level tiling strategy. In this solution the I/O subsystem keeps a copy of all the points and 476 partitions. At each iteration, during the *populate partitions* and *compute centroids* phases, each 477 computing cluster repeatedly downloads chunks of points from the I/O subsystem. These chunks 478 are small enough to fit into the available local memory. After these points are processed, they are 479 discarded to make space for the next chunk. This download/process/discard process is repeated 480 at each iteration until all points are processed. At this point the results for the current iteration are 481 uploaded to the I/O subsystem. Then, the I/O subsystem broadcasts the partial results to every 482 computing cluster and the next iteration begins. 483

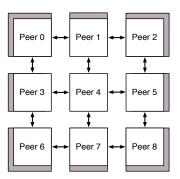

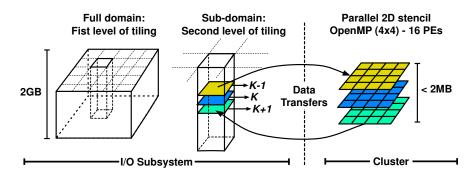

Figure 7: Multi-level tiling strategy to exploit the memory hierarchy of MPPA-256.

# 484 4.3. Seismic Wave Propagation

Performing stencil computations on the MPPA-256 processor is a challenging task. This class of numerical kernels has an important demand for memory bandwidth. This makes the efficient use of the low-latency memories distributed among compute clusters indispensable. In contrast to standard x86 processors, in which it is not uncommon to find last-level cache sizes of tens of megabytes, the MPPA-256 has only 32 MB of low-latency memory divided into 2 MB chunks spread throughout the 16 compute clusters.

The 3D data required for seismic wave modeling do not fit in those low-latency memories. Therefore, we need to design efficient master-to-slave and slave-to-master communications to make use of the 2 GB of memory available on the I/O subsystem and carefully overlap communications with computations to mask communication costs. We implement a two-level algorithm that decomposes the problem with respect to the memory available on both the I/O subsystem and the compute clusters. Figure 7 shows the algorithm.

The three dimensional structures corresponding to the velocity and stress fields are allocated 497 on the I/O subsystem to maximize the problem size that can be simulated. Next, we divide the 498 global computational domain into several subdomains corresponding to the number of compute 499 clusters involved in the computation. This decomposition is performed along the horizontal 500 direction providing a first level of data-parallelism. To respect the width of the stencil (fourth-501 order), we maintain an overlap of two grid points in each direction. These regions, called ghost 502 zones, are updated at each stage of the computation with point-to-point communications between 503 neighboring clusters. This decomposition is rather similar to the description provided in section 504 3.3.3. Unfortunately, this first level of decomposition is not sufficient as three-dimensional tiles 505 do not fit into the 2 MB of memory available on each compute clusters. 506

A second level of decomposition is therefore required. This is performed along the vertical 507 direction as we tile each three-dimensional subdomain into 2D slices. This leads to a signifi-508 cant reduction in memory consumption for each cluster but requires maintaining a good balance 509 between the computation and communication. Indeed the procedure relies on a sliding window 510 algorithm that traverses the 3D domains using 2D planes and overlaps data transfers with com-511 putations. This could be viewed as an explicit prefetching mechanism as the 2D planes required 512 for the computation at one step are brought to the clusters during the computation performed at 513 previous steps. Additionally, this vertical tiling strategy allows us to benefit from the symme-514 try of the domain in the horizontal directions. The costly absorbing boundary conditions grid 515

points located at the bottom of the domain are therefore evenly distributed among the computingclusters.

The number of planes prefetched in advance is parameterizable and its maximum value de-518 pends on the problem dimensions and the amount of available memory on each compute cluster. 519 To better exploit the NoC, we carefully select the NoC node on the I/O subsystem with which the 520 compute cluster will communicate. This choice is based on the NoC topology and aims at reduc-521 ing the number of hops necessary to deliver a message. Moreover, the prefetching scheme also 522 allows us to send less messages containing more data, which has been empirically proven to be 523 more efficient than sending several messages of smaller size. OpenMP directives are employed 524 by clusters to compute 2D problems with up to 16 PEs in parallel. 525

# 526 5. Experimental Results

In this section, we present performance and energy efficiency evaluations for the experimental platforms. These evaluations were conducted by the execution of parallel and distributed versions of the presented applications. We begin by introducing our energy consumption measurement methodology along with the metrics used to analyze the results on all platforms. Then, we compare their energy and computing performance.

### 532 5.1. Measurement Methodology

We use two important metrics to compare the energy and computing performance of different multicore and manycore platforms: *time-to-solution* and *energy-to-solution*. Time-to-solution is the time spent to reach a solution for a given problem. In our case, this is the overall execution time of the parallel/distributed version of the applications. Energy-to-solution is the amount of energy spent to reach a solution for a problem. Thus, the ratio between energy-to-solution and time-to-solution yields the average power consumed during the application execution.

Table 1 lists the average power consumed by each one of the platforms used in our exper-539 iments during the execution of the parallel and distributed versions of the applications. Even 540 though the Altix UV 2000 features 24 Xeon E5 processors, it consumes less than 24 times the 541 power observed on Xeon E5. This is an expected phenomenon because Xeon E5 runs a multi-542 threaded version of the applications whereas Altix UV 2000 runs their distributed counterparts. 543 Distributed versions experience periods of low processor usage as, for example, those during the 544 task request/response cycle and those related to load imbalance. This will be further discussed in 545 Section 5.5). 546

|                | Xeon E5 | Altix UV 2000 | Exynos 5 | <b>MPPA-256</b> |

|----------------|---------|---------------|----------|-----------------|

| TSP            | 67.9 W  | 1,418.4 W     | 5.3 W    | 8.3 W           |

| <b>K-Means</b> | 61.5 W  | 1,420.3 W     | 5.2 W    | 9.6 W           |

| Ondes3D        | 57.5 W  | 1,353.0 W     | 4.6 W    | 8.4 W           |

Table 1: Average power consumption of the 4 processors while running the applications.

The power consumed by each processor was obtained using the same approach. Both Xeon E5 and Altix UV 2000 feature Intel Sandy Bridge microarchitecture, which has Running Average Power Limit (RAPL) energy sensors. This allows us to measure the power consumption of

550 CPU-level components through Machine-Specific Registers (MSRs). We used this approach to

<sup>551</sup> obtain the energy consumption of the whole CPU package including cores and cache memory

<sup>552</sup> (named RAPL PKG domain). Similarly, MPPA-256 and Exynos 5 also possess hardware sensors

to measure power consumption of the entire chip. Power measurements using this approach are

very accurate as shown in [29, 30].

|         | Small                | Medium               | Large                   |

|---------|----------------------|----------------------|-------------------------|

| TSP     | 16 cities            | 18 cities            | 20 cities               |

| K-Means | 16,384 points        | 32,768 points        | 131,072 points          |

|         | 512 centroids        | 512 centroids        | 512 centroids           |

| Ondes3D | 16x16x16 grid points | 48x64x48 grid points | 128x128x128 grid points |

#### Table 2: Problem sizes.

We also defined three input problem sizes for all applications (Table 2). These problem sizes were chosen based on the execution time on all platforms and amount of memory needed. For instance, we used a small problem size when running the applications with low thread counts in order to obtain the results in a reasonable time<sup>1</sup>. Each experiment was repeated as many times as needed to ensure a relative error inferior to 2% with 95% statistical confidence using Student's t-distribution.

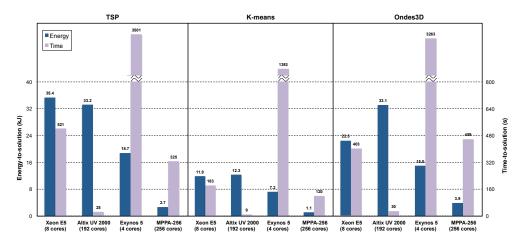

# 561 5.2. Overall Results

Figure 8 compares both time-to-solution (right y-axis) and energy-to-solution (left y-axis) metrics on all processors. Since we used every core of each processor in these experiments, we executed the applications with *large* problem sizes.

Figure 8: Time and energy-to-solution comparison between multicore, NUMA and manycore processors.

<sup>&</sup>lt;sup>1</sup>The large problem size along with very low thread counts takes several hours on embedded processors due to their low clock frequency.

Time-to-Solution. As expected, applications on Exynos 5 presented the highest execution 565 times among all platforms, being from 6.7x (TSP) up to 8.1x (Ondes3D) slower than Xeon E5. 566 The reason for that is threefold: (i) it has considerably lower clock frequency than Xeon E5; (ii) 567 Xeon E5 is a performance-centric processor that is tuned far more for speed than for low power 568 consumption; and (iii) Xeon E5 profits from its higher parallelism, since all applications scale 569 considerably well as we increase the number of threads. MPPA-256 presented better execution 570 times than Xeon E5 on TSP and K-Means, being 1.6x and 1.5x faster respectively. Even though 571 the clock frequency of MPPA-256 PEs is lower than that of the Xeon E5 cores, this embedded 572 processor achieved better performance. Once again, this is due to the inherent characteristic 573 of these applications. On TSP, peers only need to broadcast data when a new shortest path is 574 found. On K-Means, peers communicate more often but this application still performs more 575 computation than communication. 576

An optimized implementation of the seismic wave propagation algorithm has been consid-577 ered as a baseline for our evaluations. As detailed in Section 3.3, the shared-memory implemen-578 tation relies on efficient data and thread mapping strategies in order to reduce both the NUMA 579 penalty and the load imbalance. It is well known that stencil-based computations like finite differences method applied to seismic wave propagation achieve a low fraction of the peak performance on standard processors such as x86. This is mainly due to the huge demand for memory 582 bandwidth typical for this class of algorithms. On average, 30% of peak performance is reported 583 for such implementations [31]. A detailed characterization of this behavior taking into consider-584 ation both the architecture and the algorithms is given by the roofline model [32]. Nonetheless, 585 a more detailed discussion on the peak performance on the MPPA-256 architecture would require 586 revisiting the roofline model which is out the scope of this paper. Our analysis confirmed our 587 expectation that an important share of Ondes3D execution time is spent in communications. Al-588 though the prefetching scheme considerably hides the communication costs on MPPA-256, the 589 latency and bandwidth of the NoC still hurts its performance, resulting in an execution time ap-590 proximately 10% worse on MPPA-256 compared to Xeon E5. Not surprisingly, Altix UV 2000 plat-591 form presented the best execution times, since it has 24 performance optimized general- purpose 592 multicore processors. We further discuss the scalability results on Altix UV 2000 and MPPA-256 in 593 Section 5.4. 50/

Energy-to-Solution. Both Exynos 5 and MPPA-256 presented better energy-to-solution than

the other platforms. However, the low degree of parallelism available on the ARM processor

was a clear disadvantage for Exynos 5. Even though this processor consumes less power than

the others, it ends up executing the applications during a longer period of time. This results

in a higher energy consumption compared to MPPA-256. Overall, MPPA-256 achieved the best

energy-to-solution results, reducing the energy consumed by other platforms on TSP, K-Means

and Ondes3D in at least 6.9x, 6.5x and 3.8x, respectively.

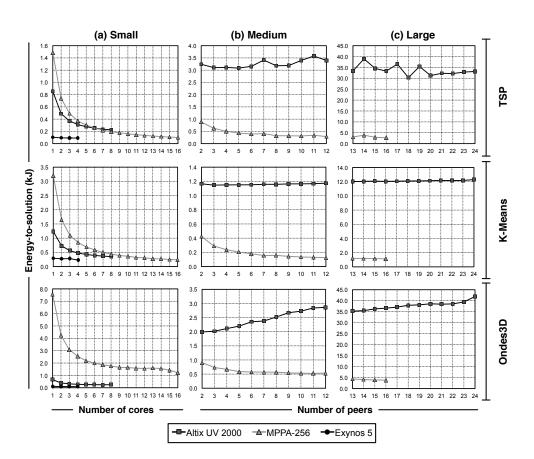

#### 602 5.3. Energy Efficiency

In the previous section, we showed that MPPA-256 presented the best energy-to-solution re-603 sults among all platforms. The main reason is that MPPA-256 offers a high parallelism and yet 604 has a low power consumption. In this section, we intend to look in more detail at the energy 605 efficiency of all platforms when we vary the number of cores. We first compare the energy-to-606 solution of all applications when varying the number of cores from 1 to the maximum number of 607 cores available in each processor (Figure 9a). In other words, we compare the energy-to-solution 608 obtained with a single processor of Altix UV 2000 (which is actually the Xeon E5), Exynos 5 and 609 a single compute cluster of MPPA-256 (in this case, we vary the number of PEs). For these tests, 610

Figure 9: Energy-to-solution comparison on all platforms with three problem sizes.

we used a small problem size due to time constraints. Then, we compare the energy-to-solution on Altix UV 2000 and MPPA-256 when varying the number of peers (*i.e.*, processors on Altix UV 2000 and compute clusters on MPPA-256), while using the maximum number of cores available on each Altix UV 2000 processor (8 cores) and MPPA-256 clusters (16 PEs). We used a medium problem size to compare the energy-to-solution from 2 to 12 peers (Figure 9b) and a large problem size for more than 12 peers (Figure 9c). Note that the MPPA-256 architecture is limited to 16 peers, therefore we only show the results for more than 16 peers on Altix UV 2000.

Varying the Number of Cores. Exynos 5 achieved the best energy-to-solution for the small 618 problem size in all applications. Figure 9a shows this behavior. The reasons for that are twofold. 619 First, Exynos 5 is the least power hungry processor among all the experimental platforms. Sec-620 ond, the problem size used in this experiment is too small to scale past 4 cores. When we compare 621 the energy efficiency of a single Altix UV 2000 processor against a single MPPA-256 cluster, we 622 notice that Altix UV 2000 outperformed MPPA-256 with low core counts on TSP and K-Means. For 623 more than 8 cores, however, the MPPA-256 cluster outperformed the Altix UV 2000 processor. This 624 comes from the fact that the power consumed by a single Altix UV 2000 processor considerably 625 626 increased as we increased the number of used cores whereas the power consumed by a single

MPPA-256 cluster remained practically unchanged. The only exception occurred on Ondes3D. In this case, MPPA-256 consumed much more energy than the Altix UV 2000 processor because communications on MPPA-256 could not be overlapped with computations using small problem sizes on Ondes3D. Moreover, the NoC bandwidth achieved in this case is poor, since we only perform 1-to-1 communications between the I/O subsystem and a single cluster.

Varying the Number of Peers. The gap between the energy consumed by Altix UV 2000 and 632 MPPA-256 became more important as we increased the number of peers. From 2 to 12 peers 633 (Figure 9b), MPPA-256 consumed at least 2.3x less energy than Altix UV 2000. This gap was 634 even larger from 13 to 16 peers with a large problem size (Figure 9c): in this case, MPPA-256 635 consumed on average  $\sim 11x$  less energy than Altix UV 2000. Once again, the rationale behind that 636 comes from the high energy cost associated to the Altix UV 2000 processors: adding one Xeon E5 637 processor usually increases the overall power consumption of Altix UV 2000 by  $\sim 60$  W on average 638 whereas adding one MPPA-256 cluster increases the overall power consumption of MPPA-256 by 639 ~0.3 W. 640

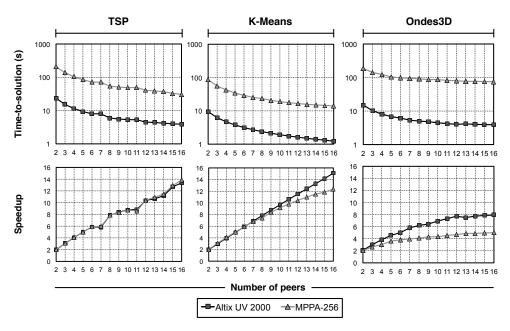

#### 641 5.4. Scalability

So far, we have only compared the energy-to-solution of MPPA-256 and Altix UV 2000, showing that the former consumed far less energy than latter to solve the same problems. Figure 10 643 illustrates the time-to-solution gap between them for a *medium* problem size when considering 644 an equal number of resources (peers) as well as the comparative speedup between the architec-645 tures. The speedup calculation was based on the effect that an increase on the number of peers 646 has on performance. For that reason, and to maintain consistency throughout our comparisons, 647 we employed as the baseline the execution time of the multi-threaded algorithms using a single 648 peer. In other words, we compared the performance of the distributed algorithm using different 649 numbers of fully utilized peers to that of a parallel version using all the resources of single peer, 650 *i.e.*, with no inter-peer communications. We measure, therefore, the scalability of the distributed 651 version of the algorithms and not that of the of the multi-threaded version. Detailed scalability 652 evaluation analysis for the multi-threaded algorithms can be found in the base works presented 653 in Section 3. 654

Overall, the distributed version of the applications scaled considerably well and execution times showed similar trends on both platforms. However, Altix UV 2000 was from 9x up to 13x faster than MPPA-256. This result was expected, since peers mean processors running at full speed (2.4 GHz) on Altix UV 2000 whereas they represent blocks (compute clusters) of the MPPA-256 processor running at 400 MHz. In other words, we are comparing sets of entire processors on Altix UV 2000 against subsets of a single MPPA-256 processor. We also observed similar performance gaps with other problem sizes.

The near-linear speedups of TSP and K-Means on both architectures show that, although 662 the actual implementations of the evaluated applications were adapted to accommodate each 663 platform's idiosyncrasies, they in fact display good and similar scalability. The exception of 664 Ondes3D can be explained by the amount communications performed by this algorithm. While 665 TSP and K-Means are CPU-bound and communicate at regular but not so frequent intervals, 666 communication on the Ondes3D is much more intensive. The weak scalability past six peers 667 demonstrates the toll imposed by these communications to the NUMA interconnections on Altix 668 UV 2000 and to the NoC on MPPA-256. 669

Moreover, in order to avoid NUMA effects on the Altix UV 2000 platform and ensure good execution performance, we had to employ some additional runtime optimizations. For all applications we employed thread-pinning [33]. Since the TSP was implemented using POSIX threads,

Figure 10: Time-to-solution and speedup comparison between Altix UV 2000 and MPPA-256.

we used Linux's specific system calls to ensure that threads would not be migrated during the 673 execution of the application. K-Means and Ondes3D used OpenMP to implement parallelism, 674 therefore in these cases we employed the GOMP\_CPU\_AFFINITY environment variable to ensure 675 threads were correctly bound to the available cores. Additionally, we specially modified the ini-676 tialization phase of the applications so that the first-touch strategy (Linux's default) could suitably 677 place the allocated memory on the NUMA nodes. For that, each application would make each 678 thread initialize (either with the actual value or with a dummy value when initialization had to 679 be centralized) each private region of memory. 680

### 681 5.5. Irregularity

In the last sections, we analyzed the energy-to-solution and the scalability of the distributed versions of all applications on both Altix UV 2000 and MPPA-256. The results showed that our distributed solutions scaled well, which indicates that the inherent irregularities of each application were satisfactorily handled.

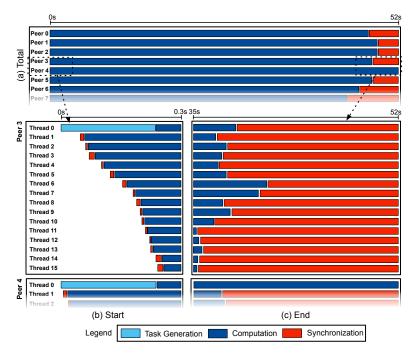

However, Figure 9a and Figure 9b reveal some points where the energy-to-solution abruptly increases (*e.g.*, from 6 to 7 and from 13 to 14 peers) in the TSP. In these cases, the addition of a peer incurred performance losses (higher execution times). In order to investigate this peculiar behavior, we traced the execution of the distributed version of TSP. Figure 11 shows the execution traces obtained on Altix UV 2000 while running the TSP with 14 peers.

Figure 11a shows a global view of the execution aggregated per peer. At the beginning (Figure 11b), one thread in each peer asks a master peer for partitions and starts populating the local pool of tasks. As tasks become available, other threads in the same peer can start the computation. Once the thread assigned to populate the local pool of tasks finishes its job, it also starts the computation. Afterwards, as the peers run out of work, they ask a master peer

Figure 11: Execution traces of TSP on Altix UV 2000.

for more partitions. This strategy works fairly well throughout most of the execution. However, in some cases the load may become imbalanced at the end of the execution. Figure 11c shows what happens inside the peers. In this case, only peer 4 keeps processing for a long time while other peers are running out of tasks. This happens because the last task associated to Thread 0 from Peer 4 takes much longer to be completed. This problem can be reduced with a workstealing strategy inside each peer, so that threads can steal segments of this big task to improve parallelism. However, we leave this optimization for a future work.

#### 703 6. Related Work

Many works have been focusing on analyzing the performance and energy efficiency of low-704 power multicore processors. Padoin et al. [34] compared an ARM Cortex-A9 1.0 GHz dual-705 core processor from Texas Instruments to two multiprocessors: one composed of two quad-core 706 2.4 GHz Intel Xeon E5 processors and the other composed of four 2.0 GHz 8-core Xeon X7 707 processors. They analyzed different metrics such as time-to-solution, peak power and energy-to-708 solution using 6 benchmarks from the NAS Parallel Benchmarks (NPB). Their results showed 709 that the ARM processor outperforms Xeon X7, considering the energy-to-solution metric, for 710 most of the analyzed benchmarks. However, the Xeon E5 had the best energy-to-solution among 711 the three processors. 712

*Göddeke et al.* [3] also conducted a comparison between ARM and x86 architectures using different classes of numerical solution methods for partial differential equations. They evaluated

weak and strong scalability on a cluster of 96 ARM Cortex-A9 dual-core processors and demonstrated that the ARM-based cluster can be more efficient in terms of energy-to-solution compared to a cluster of Intel Xeon X5550 processors. Similarly, *Ou et al.* [35] compared the energy efficiency of a ARM-based cluster against an Intel X86 workstation on three applications: a web server, an in-memory database and a video transcoding. They concluded that energy/efficiency ratio of the ARM cluster against the Intel workstation depend on the application and may vary from 1.21 up to 9.5.